服务热线

0755-83212595

时间:2020/8/11 阅读:5091 关键词:MOS管

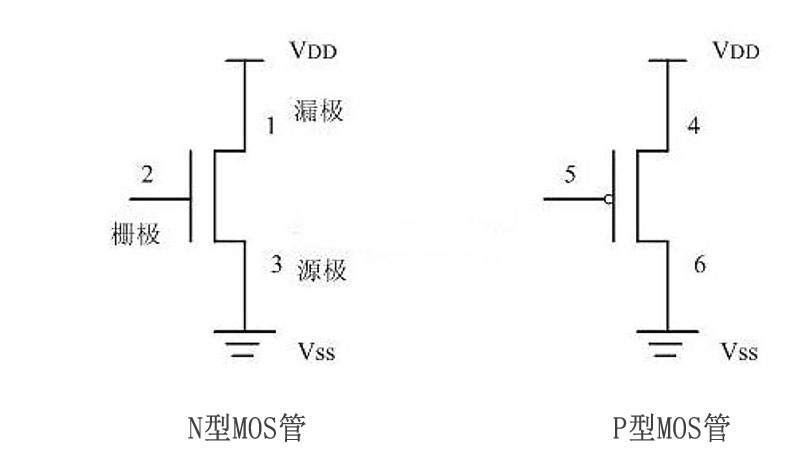

MOS管场效应管通过搭配可构成各种门电路,74系列芯片电路如下图所示:

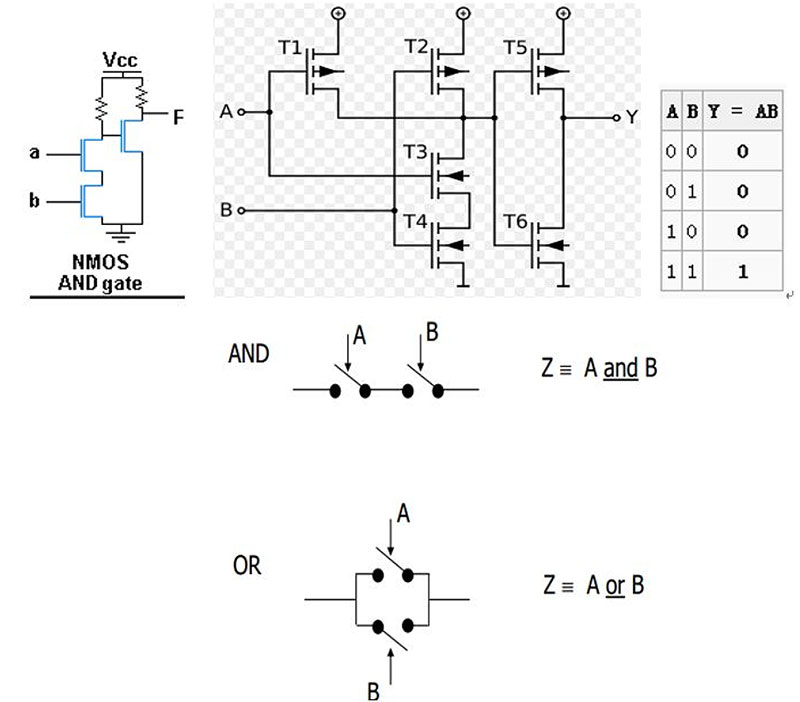

MOS管如何构成基本与门、或门电路与门

构成:六个MOS管,与门工作如下图所示:看真值表输入输出对应关系。

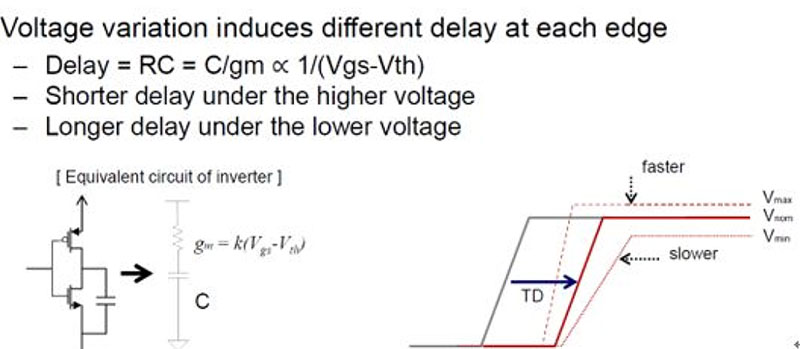

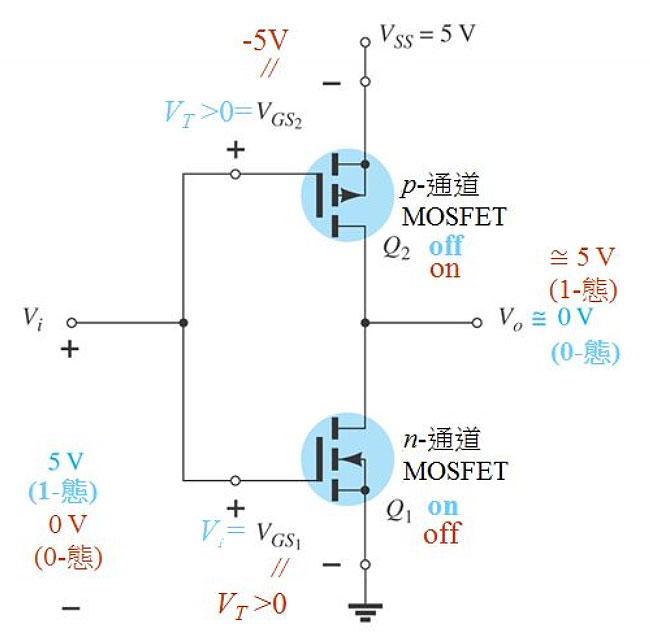

反相器电路:如下图所示:输入和输出状态相反,称之反相器。

输入Vi=低电平:上管导通,下管截止,输出=高电平;

输入Vi=高电时:上管截止,下管导通,输出为低电平。

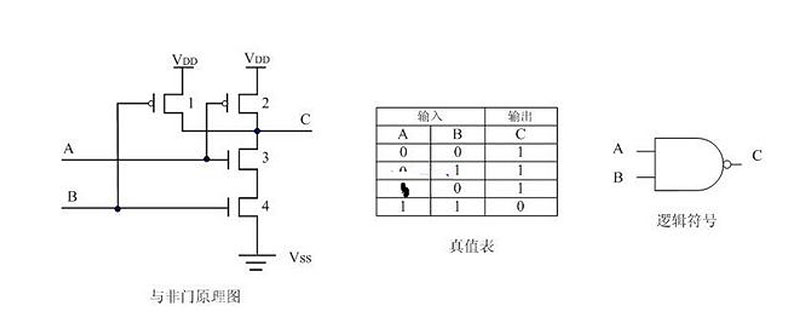

与非门的电路如下图所示:与非门是同为零,异为一。

A,B输入=低电平:1,2管导通,3,4管截止,C端电压与Vdd一致,输出高电平;

A输入高电平,B输入低电平:1,3管导通,2,4管截止,C端电位与1管的漏极保持一致,输出高电平。

A输入低电平,B输入高电平:2,4导通,1,3管截止,C端电位与2管的漏极保持一致,输出高电平。

当A,B输入=高电平:1,2管截止,3,4管导通,C端电压与地一致,输出低电平。

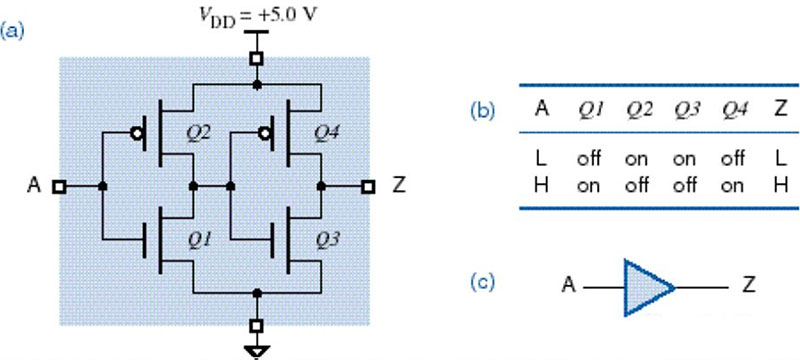

CMOS管缓冲器buffer,缓冲器跟反相器是对立的,缓冲器输入与输出相同,反相器输入与输出相反。

Q1+Q2组成反相器,Q3+Q4组成反相器,相当反了两次相,因此还原了。

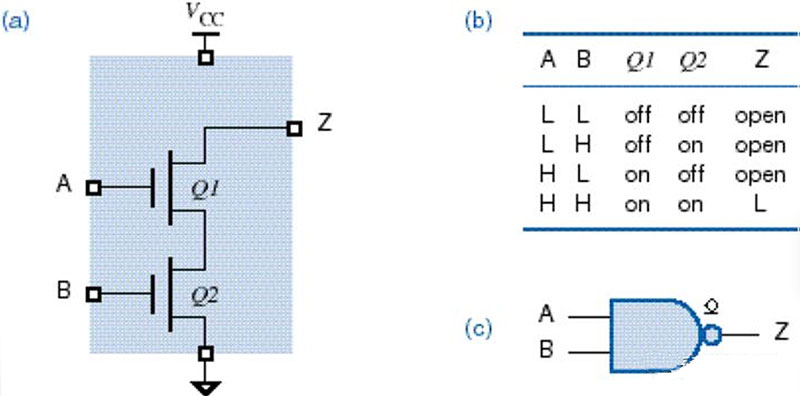

漏极开路电路:应用于主芯片GPIO口,单片机GPIO口,

它是高阻态,需接上拉电阻;

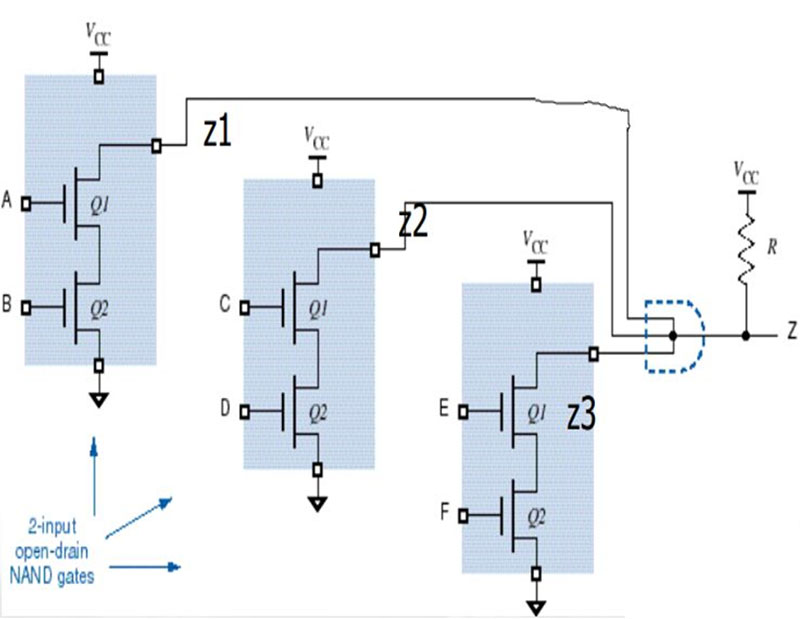

漏极开路门应用-线与逻辑 Z=z1z2z3

“线与”逻辑:多个逻辑单元输出三极管+共用一个上拉电阻+一个逻辑单元输出低电平,即集电极(漏极)开路输出MOS管导通,输出低电平;

全部单元截止,输出端被上拉电阻置为高电平,应用于逻辑仲裁等电路系统。