服务热线

0755-83212595

MOS场效应管导通损耗Pon计算公式-MOS场效应管知识-竟业电子

MOS场效应管导通损耗Pon计算公式-MOS场效应管知识-竟业电子

时间:2021/1/20键词:MOS场效应管

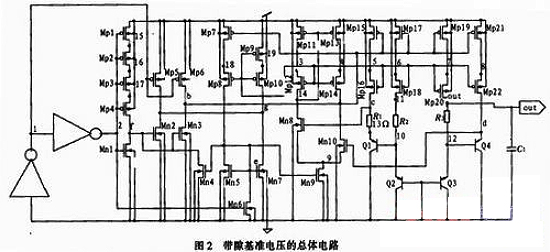

低温漂CMOS的电源抑制比及启动电路-MOS场效应管应用-竟业电子

低温漂CMOS的电源抑制比及启动电路-MOS场效应管应用-竟业电子

时间:2021/1/19键词:MOS

ESD击穿mos场效应管分析-mos场效应管保护电路失效-竟业电子

ESD击穿mos场效应管分析-mos场效应管保护电路失效-竟业电子

时间:2021/1/18键词:mos场效应管

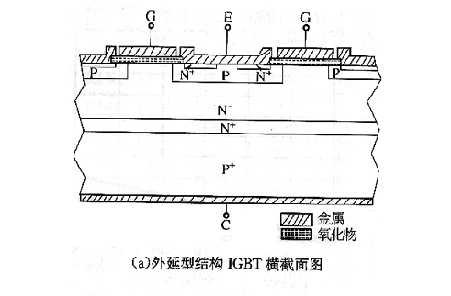

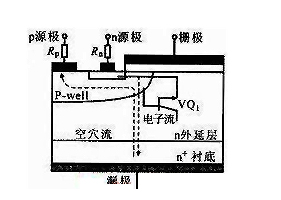

BIMOS场效应管芯片是什么及分类分析-MOS场效应管应用-竟业电子

BIMOS场效应管芯片是什么及分类分析-MOS场效应管应用-竟业电子

时间:2021/1/15键词:MOS场效应管

mos场效应管门极电压注意事项-mos场效应管应用-竟业电子

mos场效应管门极电压注意事项-mos场效应管应用-竟业电子

时间:2021/1/14键词:mos场效应管

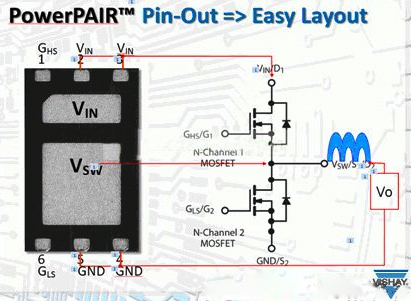

PowerPAIR封装特点-MOS场效应管双芯片封装-竟业电子

PowerPAIR封装特点-MOS场效应管双芯片封装-竟业电子

时间:2021/1/13键词:MOS场效应管

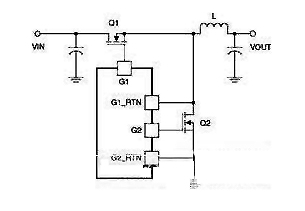

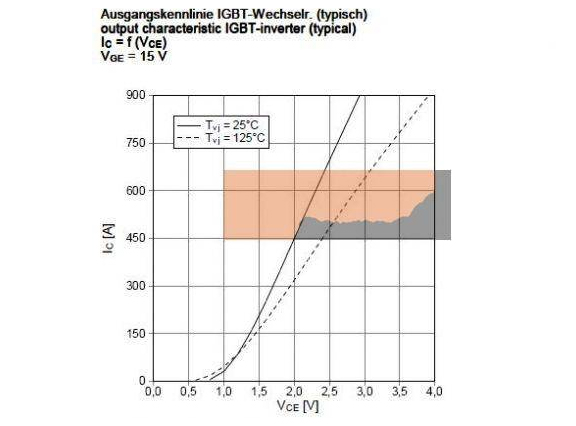

MOS场效应管与IGBT并联使用满足条件-MOS场效应管应用-竟业电子

MOS场效应管与IGBT并联使用满足条件-MOS场效应管应用-竟业电子

时间:2021/1/12键词:MOS场效应管

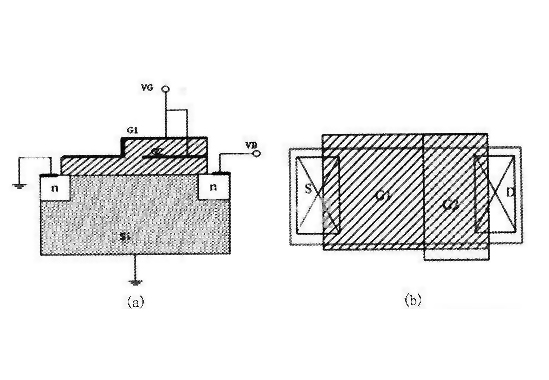

叠栅MOS场效应管是什么及结构优势-MOS场效应管应用-竟业电子

叠栅MOS场效应管是什么及结构优势-MOS场效应管应用-竟业电子

时间:2021/1/11键词:MOS场效应管

MOS场效应管抗SEB能力优化-MOS场效应管应用-竟业电子

MOS场效应管抗SEB能力优化-MOS场效应管应用-竟业电子

时间:2021/1/8键词:MOS场效应管

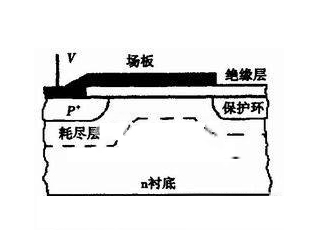

高压VDMOS场效应管横向结构设计分析-MOS场效应管应用-竟业电子

高压VDMOS场效应管横向结构设计分析-MOS场效应管应用-竟业电子

时间:2021/1/7键词:MOS场效应管