时间:2021/10/21 阅读:7682 关键词:MOS场效应管

MOS场效应管 IC gate charge电荷量与switching特性

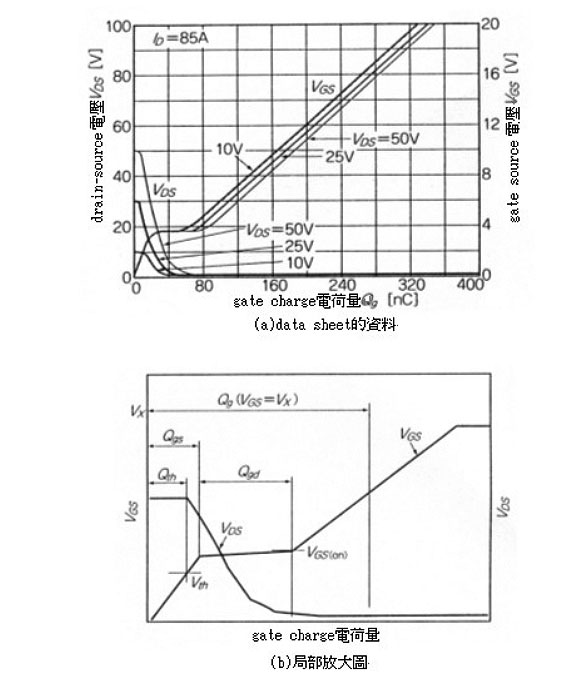

如下图所示输入动态(dynamic) 特性,

如从V GS =0V到V th 的充电期间为Q th ,curve变成完全平坦时的点,让source-gate间容量结束充电称为Q gs 。

显示从该点开始drain-source间的电压变化非常激烈,归返容量C ress 作为mirror容量也有变大趋势,充电期间会使该平坦部位的mirror容量成为Q gd ,从该处到2SK3418规定的10V驱动电压V gs 点,则变成total gate charge量Q g ,V gs =10V时的Q g ,大约是183nC。

由于Q g 驱动gate所以它是决定gate峰值电流i g(peak) ,与驱动损失P (driveloss) 等特性的重要参数,峰值电流i g(peak) 与驱动损失P (driveloss) 可用下式表示:

i g(peak) = Q g / t-

t = Q g (R s +R g ) / V GS

P (driveloss) = ƒ Х Q g Х V GS

如动作频率ƒ =20kHz低频动作,利用10V的V gs 驱动时,上公式求得驱动损失大约是36.6mW;

动作频率ƒ= 200kHz时驱动损失则变成 。

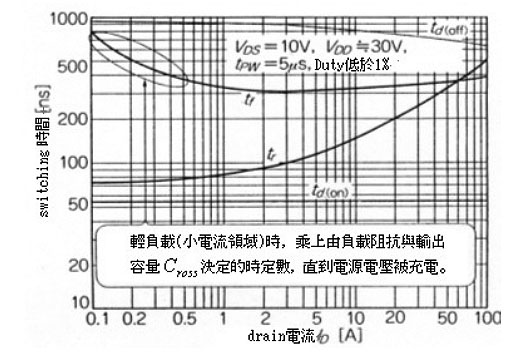

switching特性

如图Q gd 对电源电压有依存性,下降时间t可用公式t = Q g (R s +R g ) / V GS

求得近似值:Q gd 与gate内部阻抗R g 是左右switching特性的重要参数;

R s 是使驱动MOS场效应管 IC进行放电的信号源阻抗,为了使功率MOS场效应管 作高速switching,因此必需抑制驱动端的R s 。

然而t ƒ 在小负载电流亦即轻负载时,部份领域无法控制R s 与R g ,主要原因是轻负载时,t ƒ 取决于drain负载阻抗(impedance) 与drainsource容量。

如下图所示switching特性,图中实线筐围部位是利用C oss (Q oss ),与负载阻抗(impedance) R Z 两者的时定数决定的领域,该资料是用gate的50Ω信号源阻抗 驱动时的特性值,如果改用R s 极小的阻抗驱动还可以使速度加快,不过轻负载领域的速度同样无法控制。

重视轻负载领域的速度时,可以选择输出容量C oss 较小的元件,不过需注意的是这种情况,C oss 与上述 一样C iss ,C rss ,对drain与source之间的电压V DS 具有依存性,因此V DS =0V条件下抑制C oss 的值是非常重要的步骤之一。

此外Q gd 与Q g 在设计高频动作损失时,也是极重要的项目之一。

类似ƒ=100kHz以上高速动作的应用设备,一般而言低R on Q g 或是低R on Q gd 都可视为高性能元件,不过低gate阻抗R g 也很重要。

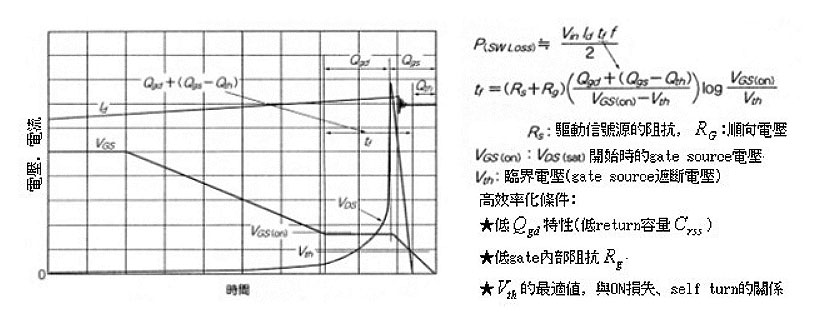

低switching损失的主要参数tƒ

如下图所示L负载switching的turn OFF波形与各参数的关系。支配L负载损失的下降时间tƒ,是用图右侧的计算公式表示。

根据计算公式可知tƒ随着V th 值改变,因此高速性的应用设备必需设法提高元件的V th 。最近几年某些厂商提供的技术资料中,波形中的Q gd +(Q gs -Q th )当作W sw 记载,这对比较、评鉴switching特性而言,算是提供相当高精度的佐证资料。

如下图V th 越高(Q gs -Q th )部份越窄,下降时间tƒ则变快,不过gate的寄生电感若很大的话,就无法在规定时间内使式(4)的gate电流i g 充放电。

source与drain之间内建二极管的特性

如下图所示内建二极管顺向电压V SD 与顺向电流的特性,本二极管的额定电流I DR 与顺向drain额定电流I D 值相同。

有关二极管的特性,当gate驱动电压为0偏压(V GS =0)时,它的顺向电压特性与一般二极管相同,不过gate驱动电压变成正偏压(N channel)时,如下第二个图所示,它是由与顺向相同的ON阻抗R DS(on) 决定,因此会出现电压下降现象,进而可以获得比SBD更低的顺向电压。

为充分发挥上述逆向特性,内建二极管的MOS场效应管 IC可以应用在下列领域:

‧防止电池逆相连接的load switch。

‧switching电源(n+1)冗长方式的hot swap电路(输出的活线插拔load switch用)

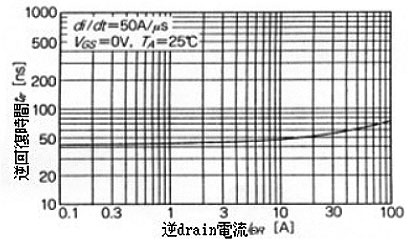

内建二极管的逆复原时间t rr 的电流I DR 特性

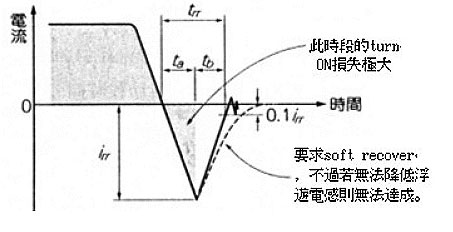

图21是内建二极管的逆复原时间t rr ,逆回复时的电流波形。类似马达驱动电路与switching电源同步整流用途的Power MOS场效应管 ,一般会要求该逆复原时间t rr 的高速性。

动作上t rr 期间由于上arm/下arm短路产生过大turn ON损失,所以控制电路系统切换上下元件switching时,先让gate信号OFF并设置deadtime(比t rr 更长的时间)。

驱动CPU core的back converter,非常重视电源的高速负载应答(response)特性,所以动作频率经常超过300kHz~1MHz,这种情况长deadtime由于该期间的二极管损失增加,因此必需在low side元件的drain与source之间将SBD并联连接,藉此降低dead time的损失。

此外上述逆复原时间t rr 会随着温度上升有增加的倾向,而且recover(下图的t b 部位)时di/dt越急峻越容易发生噪讯(noise),所以要求柔软的recover特性。

t rr 随着元件的耐压有很大的差异,60V以下低耐压元件的t rr ,介于40~60ns属于高速type; 等级大约是100ns左右;高耐压250~500V,大约是300~600ns左右,所以250V以上高耐压type必需利用寿命期(life time)控制技术,取得100ns左右高速化效果。

深圳市福田区华强北路

深圳市福田区华强北路

1019号华强广场A座9J

0755-83212595

0755-83212595

139 2389 6490 微信

postmasterr@jingyeic.com

postmasterr@jingyeic.com

全球现货一站配齐

全球现货一站配齐 原厂代理分析授权

原厂代理分析授权 闪电发货配货快

闪电发货配货快